North Carolina State University, the University of Illinois at Urbana-Champaign and Georgia Tech are forming a center that aims to speed up design and verification of microelectronic circuits and systems, reducing development costs and time-to-market for manufacturers of microelectronic products, especially integrated circuits. The center is funded for five years through the National Science Foundation’s Industry/University Cooperative Research Centers (I/UCRC) program, and by the industrial members of the center.

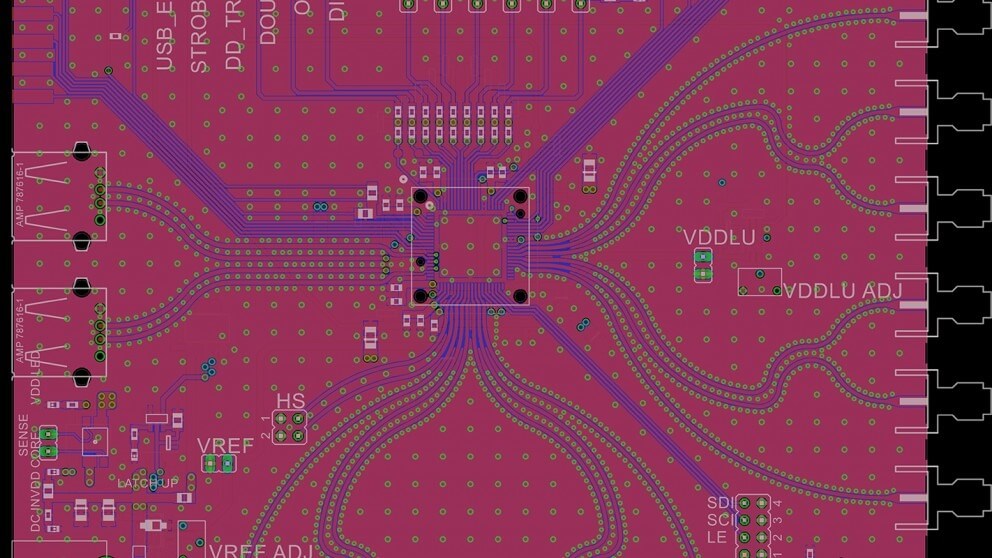

Integrated circuits, or chips, power everything from smart watches to supercomputers. The semiconductor industry – perennially one of America’s top exporters – has been searching for new ways to increase performance while reducing chip size and development cost.

The new Center for Advanced Electronics through Machine Learning (CAEML) will seek to accelerate advances by leveraging machine-learning techniques to develop new models for electronic design automation (EDA) tools, which semiconductor companies use to create and verify chip designs for mass production.

The collective goal is to create a system to make the design evaluation process much easier, says Paul Franzon, a Distinguished Professor of Electrical Engineering and CAEML site lead at NC State.

“I like to say that a silicon chip is the most complex artifact made by man,” Franzon said. “There are billions of components in a chip- it is mind-boggling. We’re creating models that help deal with these complexities, so that zwhen we design chips, we design them to work the first time.”

Currently, chip manufacturers struggle to optimize power, performance, reliability, and cost in their designs, because analyzing the mix is too computationally intensive to execute in a timely manner. Researchers aim to overcome current limitations by employing behavioral models, which look at the behavior, or output, of a chip instead of the internal processes described by physical models (which are the most commonly used kind in today’s design flows).

“When products fail qualification testing, it is usually attributed to shortcomings in the models employed by the EDA tools,” said Elyse Rosenbaum, principal investigator and a professor of electrical and computer engineering at Illinois. “Many products have to go through at least one re-spin before entering the marketplace, resulting in the loss of money and time.”

The CAEML team will create a systematic method for generating behavioral models, with which the industry has had only limited success in the past. The work will draw on deep networks, associative memories, and other research areas within the field of machine learning.

Researchers will take a comprehensive approach, developing a methodology that is applicable to large systems, with the understanding that most microelectronic systems consist of more than just a single chip. Even a “system on a chip” consists of a package as well as the semiconductor chip, and the system performance is highly affected by the interactions between the two, according to Madhavan Swaminathan, a professor and CAEML site director at Georgia Tech.

“With the interface between the chip and the package disappearing through integration, such as System-in-Package technologies, systems need to designed, modeled, and optimized holistically,” said Swaminathan. “Our goal in CAEML is to address systems in such a way that intellectual property can be protected and re-spins minimized.”

As an I/UCRC, CAEML will collaborate closely with companies, which will help evaluate and select projects. The corporate connections will enable the researchers to understand the real-world problems faced by manufacturers and provide a pipeline of ideas between academia and industry. The center’s industry members, which include major semiconductor, EDA, and networking companies, as well as government research labs, also will help fund the center’s work; currently, 11 companies have committed a total of $550,000 for the first year. NSF will contribute an additional $450,000 per year.